Highlights of C9600X-LC-56YL4C

- Apply to C9606R Chassis

- Only paired with Supervisor 2 C9600X-SUP-2 (3.2 Tbps bandwidth)

- Up to 56 ports of 50G/25G/10G, and 4 ports of 100G/40G nonblocking

- Speed is auto-negotiated depending on the inserted optics

- LAN and WAN-MACsec are performed on the CDR5M 2.0 PHY

- NOT supported with Supervisor 1 C9600-SUP-1

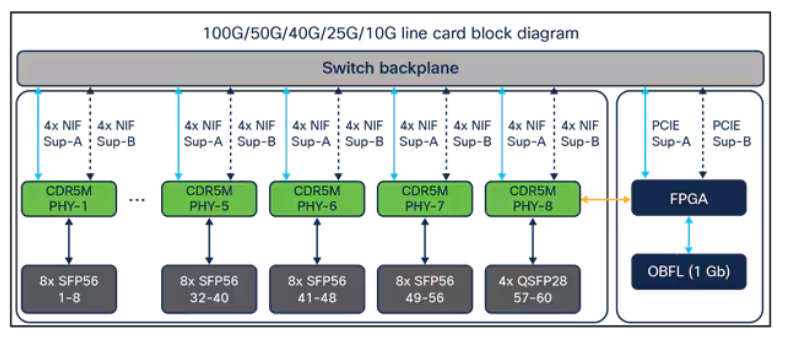

Architecture:

CDR5M 2.0 PHY is a fifth-generation 56G PAM4 x2 400G full-duplex clock and data recovery engine that provides speed transition between the ASIC and front panel. CDR5M PHY also provides MACsec/WAN-MACsec encryption at line rate.

Reviews

There are no reviews yet.